乘法器原理与硬件实现 - Vinson88 - 博客园

2022年1月18日 · 这里讨论乘法器的各种设计方法。尽管Verilog语言中有关键字signed(没有unsingned),借助其可方便地用"$*$"描述无符号数乘法和有符号乘法,但同样可根据目标需求(速度优先还是资源优先)采用

乘法器 - 维基百科,自由的百科全书

二进制的乘法器(英語: multiplier )是数字电路的一种元件,它可以将两个二进制数相乘。 乘法器是由更基本的 加法器 组成的。 乘法器作为基本的功能单元电路被广泛的应用于各种的 信号处理 和变换电路中。

数字电路设计(4)——乘法器 - 知乎 - 知乎专栏

本文将介绍几种典型的 乘法器 结构,包括阵列乘法器、改进的booth编码乘法器,以及介绍Wallace tree压缩结构对部分积求和速度的影响。 1.乘法运算过程 在数字系统中,乘法运算是以二进制的形式进行的,假设乘数为A,被乘数为B,那么写成 二进制数 为

乘法器的实现(阵列、Booth、Wallace) - CSDN博客

2022年5月10日 · 数字电路中乘法器是一种常见的电子元件,其基本含义是将两个数字相乘,并输出其乘积。与加法器不同,乘法器可以实现更复杂的运算,因此在数字电路系统中有着广泛的应用。

乘法器 - 百度百科

乘法器(multiplier)是一种完成两个互不相关的模拟信号相乘作用的电子器件。它可以将两个二进制数相乘,它是由更基本的加法器组成的。乘法器可以通过使用一系列计算机算数技术来实现。

数字IC经典电路(2)——经典乘法器的实现(乘法器简介及Verilo…

2023年3月22日 · verilog实现乘法器以下介绍两种实现乘法器的方法:串行乘法器和流水线乘法器。 1)串行 乘法器 两个N位二进制数x、y的乘积用简单的方法计算就是利用移位操作来 实现 。

- [PDF]

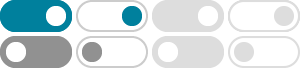

模拟乘法器 - Analog

其中一个信号为单极性,而其他信号可能为正或负,则乘法器就是一个“二象限”乘法器, 输出可能为两个极性之一(因而为“ 双极性”)。 用于产生一象限或二象限乘法器的电路可能

乘法器的设计和优化 - 知乎 - 知乎专栏

2023年7月6日 · 基本乘法过程 对于十进制的乘法,需要通过9X9乘法表来推算,而 二进制乘法 只需要看通过乘数是1还是0,来得到运算的中间结果,这也是计算机选择二进制的主要原因,基本操作如下图所示:

乘法电路 - 百度百科

乘法器(multiplier)是一种完成两个互不相关的 模拟信号 相乘作用的电子器件。它可以将两个二进制数相乘。它是由更基本的 加法器 组成的。通常的乘法计算方法是添加和位移的算法。在并行乘法器当中,相加的部分乘积的数量是主要的参数。

1. 乘法器 - Digital Lab 2024

下图展示了一个基础的乘法器结构: 整个电路包含三个寄存器(被乘数 Multiplicand、乘数 Multiplier、乘积 Product)、一个加法器和一个控制单元。我们用一个简单的二进制乘法作为例子: \(1000\times1001\) 。这是两个四位的二进制数相乘,为此我们要实现一个四位的 ...