Advanced eXtensible Interface - Wikipedia

The Advanced eXtensible Interface (AXI) is an on-chip communication bus protocol and is part of the Advanced Microcontroller Bus Architecture specification (AMBA). [1] [2] AXI had been …

Introduction to the Advanced Extensible Interface (AXI)

2019年10月17日 · The AXI specification defines the interface between a master and slave, a master and interconnect, and a slave and interconnect. In reality, interconnects contain slave …

Introduction to AXI Protocol: Understanding the AXI interface

2016年10月24日 · The protocol used by many SoC designers today is AXI, or Advanced eXtensible Interface, and is part of the Arm Advanced Microcontroller Bus Architecture …

This guide introduces the main features of Advanced Microcontroller Bus Architecture (AMBA) AXI4, highlighting the differences from the previous version AXI3. The guide explains the key …

Documentation – Arm Developer

AXI is an interface specification that defines the interface of IP blocks, rather than the interconnect itself. The following diagram shows how AXI is used to interface an interconnect component: …

AMBA AXI4 Interface Protocol - Xilinx

AMBA AXI4 (Advanced eXtensible Interface 4) is the fourth generation of the AMBA interface specification from ARM. AMD Vivado Design Suite 2014 and ISE Design Suite 14 extends the …

AMBA 4 / AMBA 3 / AMBA 2 - Arm

The AMBA 3 AXI interface specification defines the AXI protocol, which is known as the AXI3 protocol in later generations of AMBA. AXI supports five unidirectional channels with flexible …

•Provides the interface standard that enables IP reuse • Facilitates right-first-time development of multi-processor designs with large numbers of controllers and peripherals

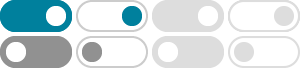

AXI4-Lite is a light-weight, single transaction memory mapped interface. It has a small logic footprint and is a simple interface to work with both in design and usage. AXI4-Stream …

Welcome to Real Digital

The “advanced extensible interface” (AXI) bus is a high-performance, point-to-point, master-slave parallel bus used to connect on-chip peripheral circuits (or IP blocks) to processor cores. The …